## RELIABILITY ENGINEERING IN RF CMOS

Guido T. Sasse

#### Samenstelling promotiecommissie:

Leden:

Voorzitter: prof.dr.ir. J. van Amerongen Universiteit Twente Secretaris: prof.dr.ir. J. van Amerongen Universiteit Twente

Promotoren: prof.dr. J. Schmitz Universiteit Twente, NXP Semiconductors

prof.dr.ir. F.G. Kuper Universiteit Twente

Referenten: dr.ing. L.C.N. de Vreede Technische Universiteit Delft

dr. P.J. van der Wel

prof.dr.ir. W. van Etten

NXP Semiconductors

Universiteit Twente

prof.dr. G. Groeseneken Katholieke Universiteit Leuven, IMEC

prof.dr.ir. A.J. Mouthaan Universiteit Twente

The work described in this thesis was supported by the Dutch Technology Foundation STW (Reliable RF, TCS.6015) and carried out in the Semiconductor Components Group, MESA<sup>+</sup> Institute for Nanotechnology, University of Twente, The Netherlands.

G.T. Sasse Reliability Engineering in RF CMOS Ph.D. thesis, University of Twente, The Netherlands

ISBN: 978-90-365-2690-6

Cover design: J. Warnaar

Printed by PrintPartners Ipskamp, Enschede

© G.T. Sasse, Enschede, 2008

## RELIABILITY ENGINEERING IN RF CMOS

## PROEFSCHRIFT

ter verkrijging van

de graad van doctor aan de Universiteit Twente,

op gezag van de rector magnificus,

prof.dr. W.H.M. Zijm,

volgens besluit van het College voor Promoties

in het openbaar te verdedigen

op 4 juli 2008 om 15.00 uur

door

Guido Theodor Sasse geboren op 29 september 1977  ${\rm te\ Lochem}$

Dit proefschrift is goedgekeurd door de promotoren:

prof.dr. J. Schmitz prof.dr.ir. F.G. Kuper

# Contents

| 1        | Inti          | roduction 1                            |

|----------|---------------|----------------------------------------|

|          | 1.1           | RF CMOS                                |

|          | 1.2           | Reliability engineering                |

|          | 1.3           | MOSFET degradation mechanisms          |

|          |               | 1.3.1 Hot carrier degradation          |

|          |               | 1.3.2 Gate-oxide breakdown             |

|          |               | 1.3.3 NBTI                             |

|          | 1.4           | Outline of the thesis                  |

| <b>2</b> | $\mathbf{RF}$ | MOS measurements 9                     |

|          | 2.1           | Introduction                           |

|          | 2.2           | RF vs. AC/DC measurements              |

|          | 2.3           | Small signal two-port characterization |

|          |               | 2.3.1 <i>s</i> -parameters             |

|          |               | 2.3.2 Calibration                      |

|          |               | 2.3.3 De-embedding                     |

|          | 2.4           | Linear one-port RF voltage generation  |

|          |               | 2.4.1 Setting the amplitude            |

|          |               | 2.4.2 Verifying linearity              |

|          | 2.5           | Conclusions                            |

| 3        | MC            | OSFET degradation under RF stress 25   |

|          | 3.1           | Introduction                           |

|          | 3.2           | RF hot carrier degradation             |

|          |               | 3.2.1 DC model                         |

|          |               | 3.2.2 AC effects                       |

|          |               | 3.2.3 Measurement setup                |

|          |               | 3.2.4 Measurement results              |

|          |               | 3.2.5 Discussion                       |

|          | 3.3           | RF NBTI degradation                    |

|          |               | 3.3.1 DC model                         |

|          |               | 3.3.2 AC effects                       |

|          |               | 3.3.3 Measurement setup                |

vi CONTENTS

|   |               | 3.3.4 Measurement results                                   |

|---|---------------|-------------------------------------------------------------|

|   |               | 3.3.5 Discussion                                            |

|   | 3.4           | Gate-oxide breakdown under RF stress                        |

|   |               | 3.4.1 DC model                                              |

|   |               | 3.4.2 AC effects                                            |

|   |               | 3.4.3 Measurement setup                                     |

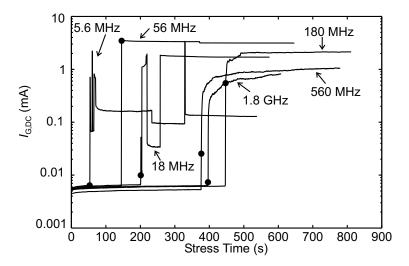

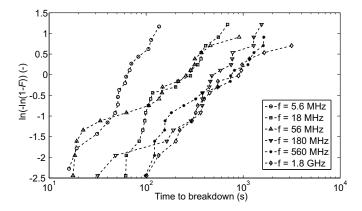

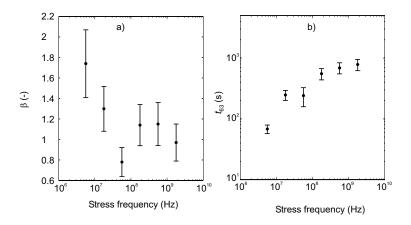

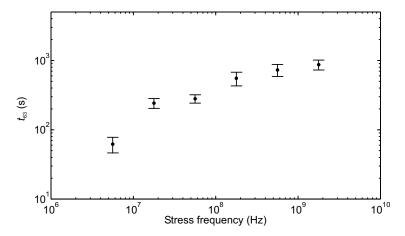

|   |               | 3.4.4 Measurement results                                   |

|   |               | 3.4.5 Discussion                                            |

|   | 3.5           | Conclusions                                                 |

| 4 | $\mathbf{RF}$ | PA lifetime prediction 51                                   |

|   | 4.1           | Introduction                                                |

|   | 4.2           | Degraded MOSFET model                                       |

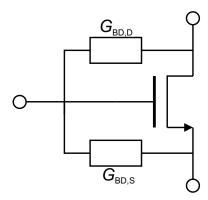

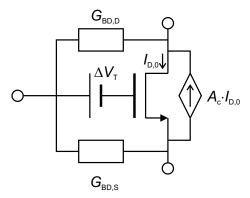

|   |               | 4.2.1 Breakdown paths                                       |

|   |               | 4.2.2 Hot carrier degradation                               |

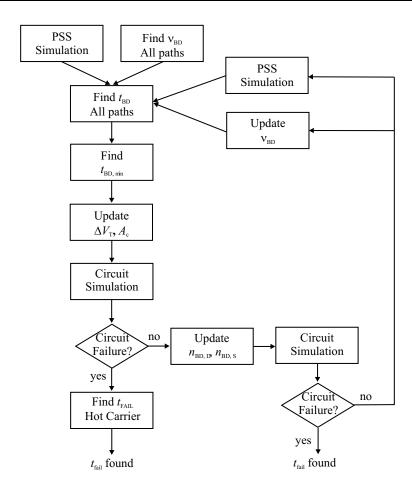

|   | 4.3           | Design of the simulator                                     |

|   |               | 4.3.1 Probability function for multiple breakdown events 60 |

|   |               | 4.3.2 Implementation                                        |

|   | 4.4           | Simulation results                                          |

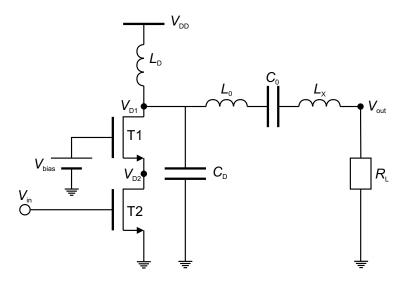

|   |               | 4.4.1 Description of the evaluated circuits 63              |

|   |               | 4.4.2 Stress conditions                                     |

|   |               | 4.4.3 Circuit lifetime prediction 69                        |

|   | 4.5           | Discussion                                                  |

|   | 4.6           | Conclusions                                                 |

| 5 | $\mathbf{RF}$ | reliability characterization 77                             |

|   | 5.1           | Introduction                                                |

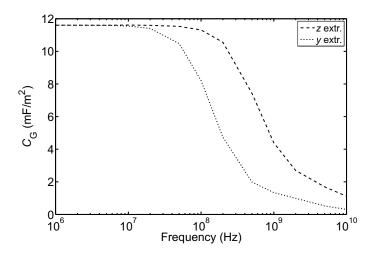

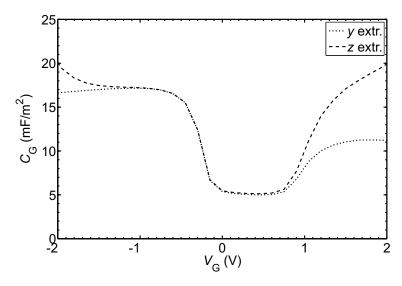

|   | 5.2           | Capacitance extraction from RF C-V measurements             |

|   |               | 5.2.1 Basics of the RF C-V technique                        |

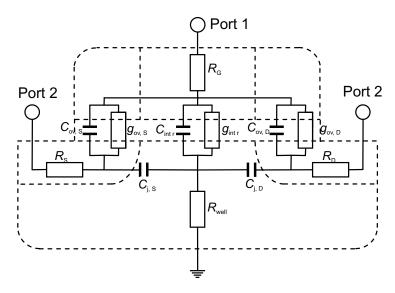

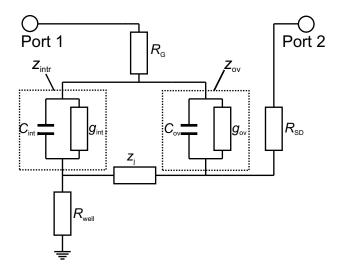

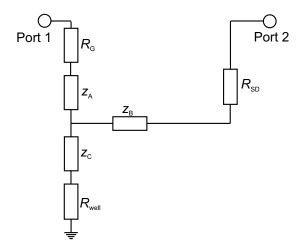

|   |               | 5.2.2 Two-port analysis of the test structure               |

|   |               | 5.2.3 Capacitance extraction methodologies                  |

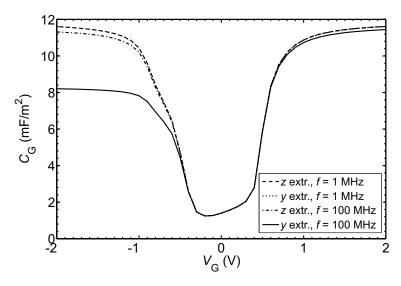

|   |               | 5.2.4 Comparison of the extraction methodologies 84         |

|   |               | 5.2.5 Discussion                                            |

|   | 5.3           | Charge pumping at radio frequencies                         |

|   | 0.0           | 5.3.1 Introduction                                          |

|   |               | 5.3.2 Measurement setup and methodology 90                  |

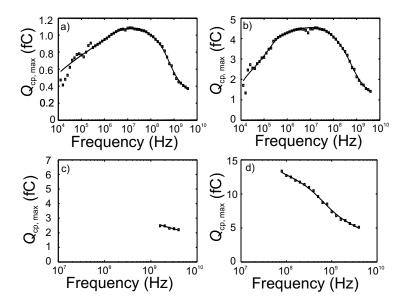

|   |               | 5.3.3 Measurement results                                   |

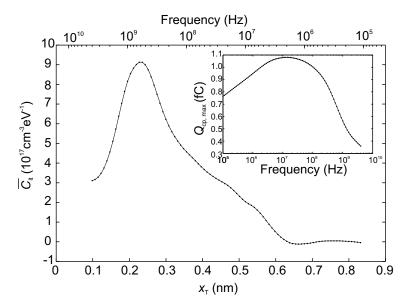

|   |               | 5.3.4 Trap Response                                         |

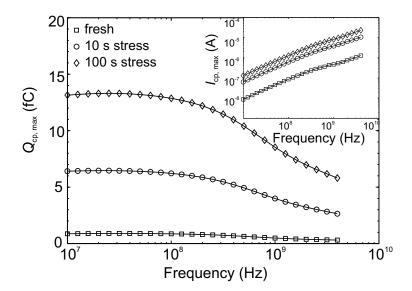

|   |               | 5.3.5 Applications of RF CP measurements                    |

|   |               | 5.3.6 Discussion                                            |

|   | 5.4           | Conclusions                                                 |

| 6 | Cor           | aclusions and recommendations 107                           |

| J | 6.1           | General conclusions                                         |

|   | -             | Recommendations for future work                             |

|   |               |                                                             |

| CONTENTS | vii |

|----------|-----|

|----------|-----|

| A         | A.1   | bration equations Error terms Calculating $V_{\mathrm{DUT,pp}}$ |  |  |  |  |  |     |   |  |  |  |     | 1 |

|-----------|-------|-----------------------------------------------------------------|--|--|--|--|--|-----|---|--|--|--|-----|---|

| Su        | mma   | ary                                                             |  |  |  |  |  |     |   |  |  |  | 125 | 5 |

| Sa        | men   | vatting                                                         |  |  |  |  |  |     |   |  |  |  | 127 | 7 |

| Lis       | st of | publications                                                    |  |  |  |  |  |     |   |  |  |  | 129 | ) |

| Dankwoord |       |                                                                 |  |  |  |  |  | 131 | L |  |  |  |     |   |

## Chapter 1

## Introduction

## 1.1 RF CMOS

The use of mobile wireless communication systems is rapidly increasing. Electronics involved in these systems are typically referred to as RF electronics. RF stands for radio frequencies, a term covering all frequencies of the electromagnetic spectrum used for transmitting radio signals. It spans from a few Hz to 100's of GHz. When dealing with present-day mobile applications the frequencies involved typically range between  $\sim\!500$  MHz and  $\sim 5$  GHz. For example the four frequency bands used for GSM communication throughout the world are located around 850, 900, 1800 and 1900 MHz. In electronics design the term RF is often used to describe only those frequencies at which design and measurement issues start to arise that are typical for the high frequencies used in mobile wireless communication systems. Throughout this thesis the term RF also reflects only these high frequencies; in chapter 2 the precise definition of RF as used in this thesis will be explained.

The IC technologies involved in wireless systems operating at such high frequencies include GaAs, SiGe, Bipolar, BiCMOS and CMOS. In earlier years CMOS was not applicable for RF electronics, but through the efforts made in scaling CMOS technology, the RF performance of CMOS has increased significantly [1]. As a consequence CMOS has become the dominating technology used for mobile wireless applications, like it has already dominated logic applications, such as CPU's, for decades. When used in RF electronics, CMOS is often referred to as RF CMOS.

The only part of mobile applications in which CMOS still does not dominate is the Power Amplifier (PA). This module is used in the transmitting end of a wireless communication system. In the PA an electromagnetic wave is generated carrying all information, such as speech or data, which is fed to an antenna. The information this wave carries must be read at the receiver end, such as the base-station of a GSM network, of the wireless communication system. For the information to be available at the receiver end, the power of this electromagnetic

2 1 Introduction

wave must be sufficiently large in order to prevent loss of information between the transmitter and the receiver.

The reason for the absence of CMOS in a PA is the fact that present-day CMOS technologies operate at relatively low voltage levels. While this may be desired for logic applications, it is easy to verify that when the maximum output voltage of a circuit is relatively low, its maximum output power will also be relatively low. This is the main bottleneck of implementing all electronics of a wireless mobile application into a single chip.

Operating the MOSFETs in an RF CMOS circuit at voltage levels exceeding nominal supply voltage may possibly be allowed. This requires a good understanding on the limitations of RF CMOS in terms of stress conditions. Lifetime specifications of CMOS are at present only well-investigated for DC and low frequency conditions. In general the reliability performance of RF CMOS is not well understood at present; designers make use of design specifications made for digital CMOS. Developing such specifications for RF CMOS may relax these design guidelines and as a consequence performance of RF CMOS electronics may be boosted. In the field of reliability engineering the topic of RF CMOS has only been addressed marginally. In this thesis new developments are described for a better incorporation of RF CMOS in the field of reliability engineering. As PA's are a critical block in terms of reliability, the developments described in this thesis were performed with a special attention to the design of reliable RF PA's.

## 1.2 Reliability engineering

Reliability engineering is an engineering field that deals with the reliability of products. Reliability, as defined in [2] is the probability of operating a product for a given time under specified conditions without failure. Reliability engineering makes it possible to set specifications on the number of products that still operate under normal use conditions years ahead in the future, thereby predicting its physical lifetime. Typically, the electronics in mobile applications have an economic lifetime of a couple of years. If it is found that the physical lifetime is far beyond what is required, designs may be adjusted in such a way that the performance of the product can be boosted. In this context the physical lifetime of a product is defined as the moment in time at which the reliability of the product has decreased below a given value. Throughout this thesis, the lifetime always refers to this physical lifetime.

A term related to reliability is *degradation*; this is used to describe the change in performance of a product or one of the components the product is composed of. If the degradation has reached a given level, the product is said to have reached its lifetime. The *degradation rate* is the speed at which this process of degradation takes place.

Physical lifetime prediction requires a good description of the reliability of the product as a function of time. For this purpose a reliability engineer has several tools, ranging from statistical algorithms to failure analysis tools. Describing the

complete set of tools used by reliability engineers lies outside the scope of this thesis. In this thesis new developments are described in three important topics of reliability engineering, with a focus on RF CMOS:

- 1. Understanding the physical processes involved in the degradation of a product. If the physical mechanisms are well understood, their effect can accurately be extrapolated to the future for making lifetime predictions. In the field of micro-electronics this so-called physics-of-failure approach is the custom way of dealing with reliability [3]. Different failure mechanisms have been found and in the next section the three typically encountered failure mechanisms in MOSFETs will briefly be discussed. In this thesis the manifestation of these degradation mechanisms under RF conditions is investigated.

- 2. Characterization of the level of degradation of a product and its components. As the degradation of a product, and the components it is composed of, under normal use conditions takes place on very long timescales, information on the degradation rate is typically obtained from accelerated stress experiments. In such experiments a product is operated under stress conditions much more severe than it would under normal operation conditions and as a consequence the degradation takes place on a timescale much smaller than the expected physical lifetime under normal operation. Assessing the amount of degradation involves the use of specifically designed characterization techniques. The development of characterization methods is an essential part of reliability engineering. In this thesis this topic will be addressed: new characterization tools are developed for the reliability evaluation of CMOS, making use of RF measurement techniques. These characterization tools may be applied in the reliability evaluation of both RF CMOS as well as digital CMOS.

- 3. Translating degradation rates of individual components to product lifetime. Even with accurate knowledge on the physical processes involved with degradation and experimentally obtained degradation rates of the different components of a product, it is not straightforward to predict product lifetime under use conditions. For this to be available use can be made of several tools. An important tool that is used, especially in the field of micro-electronics, is reliability simulation. In a reliability simulator the degradation of a product can be predicted as a function of time, based on the degradation of the individual components of the product. In this thesis the development of a new reliability simulator is described, intended to model the lifetime of PA's in RF CMOS.

While reliability engineering spans an even broader set of topics, this is a good starting point for the development of reliability engineering tools for RF CMOS. This development is what will be discussed in the following chapters.

4 1 Introduction

## 1.3 MOSFET degradation mechanisms

Several degradation mechanisms can affect the performance of CMOS circuits. In this section the three well-accepted degradation mechanisms found in the active devices in a CMOS circuit, i.e. the MOSFETs, will be described. Other degradation mechanisms may also affect the performance of CMOS circuits, but in this thesis only those mechanisms affecting the actual MOSFETs are put under investigation. All experimental verification as described in this thesis is performed on-wafer. Only individual MOSFETs are considered, thereby not investigating reliability issues related to interconnects, such as electromigration.

The degradation mechanisms discussed all affect either the gate-oxide or the interface between the gate-oxide and the silicon substrate. Important elements in all three degradation mechanisms are defects in the crystal structure of the gate-oxide. These defects are often referred to as traps; traps near the interface between the oxide and the silicon substrate are called interface traps and traps further away from the silicon substrate are called oxide traps. Interface traps are sometimes also called interface states. In the three mechanisms discussed below these traps are either being formed or they are filled with electrons or holes originating from the silicon substrate, thereby causing device degradation. A filled oxide trap causes a fixed oxide charge in a MOSFET.

## 1.3.1 Hot carrier degradation

Hot carrier degradation is the effect caused by high energetic charge carriers flowing in the channel of a MOSFET. It affects both nMOSFETs and pMOSFETs. When a MOSFET is biased in inversion and a drain-source voltage  $V_{\rm DS}$  is applied, charge carriers flow from the source region towards the drain. These charge carriers gain energy from the electric field induced by the applied  $V_{\rm DS}$ . The most energy is gained in the region alongside the channel where the lateral electric field is highest; this will be near the drain region. If one looks at the distribution of the kinetic energy of the carriers near the drain, and compares it to a population without external bias it appears that the carrier population resembles a population at a temperature higher than the temperature of the silicon. The carriers are said to have become hot. When these hot carriers have an energy sufficiently high, they may cause damage to the device. This damage can be the result of trapping of charge carriers in oxide traps or the formation of new oxide traps or interface states.

Some of the high energetic carriers do not directly cause damage to the device, but they are the origin of a substrate current  $I_{\rm sub}$  or gate current  $I_{\rm G}$ . Both these currents can be used to monitor the device degradation due to hot carrier stress.  $I_{\rm G}$  originates from Channel Hot Carriers (CHC). In CHC mode some hot carriers have gained sufficient energy to surmount the Si-SiO<sub>2</sub> barrier. These carriers may reach the gate and thereby contribute to a measurable  $I_{\rm G}$ .  $I_{\rm sub}$  results from Drain Avalanche Hot Carriers (DAHC). In this mode some hot carriers in the channel cause impact ionization, thereby generating a new electron hole pair.

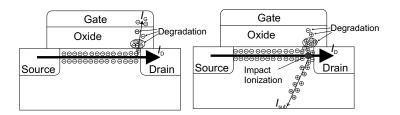

**Figure 1.1:** Illustration of CHC (left) and DAHC (right) in an nMOSFET. Electrons flow from the source towards the drain, thereby gaining kinetic energy from the applied  $V_{\rm DS}$ . Some of these carriers cause device degradation, while other contribute to a measurable  $I_{\rm G}$  (CHC mode) or  $I_{\rm sub}$  (DAHC mode).

As a consequence carriers may flow towards the substrate contact (holes in an nMOSFET an electrons in a pMOSFET), thereby contributing to a measurable  $I_{\rm sub}$ .

Both  $I_{\rm G}$  and  $I_{\rm sub}$  are indicators for the kinetic energy distribution of the charge carriers in the channel. They can be used for estimating the amount of degradation of a device, without measuring the device parameters. Accelerated stress experiments for characterizing hot-carrier degradation in MOSFETs are often performed at bias conditions for maximum  $I_{\rm sub}$  or  $I_{\rm G}$ . Also in reliability simulators use is made of  $I_{\rm sub}$  and  $I_{\rm G}$ , obtained from a circuit simulation; device degradation due to hot carriers is directly linked to these currents.

In CHC mode only carriers of one polarity are involved, while in DAHC both electrons and holes contribute to device degradation. CHC and DAHC are illustrated in figure 1.1 for an nMOSFET.

#### 1.3.2 Gate-oxide breakdown

Gate-oxide breakdown is the sudden formation of a conductive path in the gate-oxide of a MOS device. Oxide breakdown is generally considered a two-step process [4]: in the first phase a gradual build-up of damage occurs in the oxide and the second step is the sudden formation of a breakdown path. Different models for describing the degradation phase have been proposed, such as the anode hole injection [5], the anode hydrogen release [6] or the thermochemical model [7].

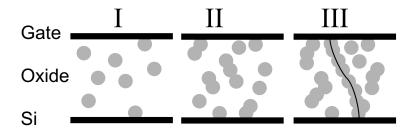

The formation of the breakdown path can be explained using percolation theory [8], as illustrated in figure 1.2. Due to a stress signal at the gate, traps are being formed inside the oxide with a certain trap generation rate. The exact position where individual traps are formed are randomly distributed; if two traps are situated close to each other, charge can easily flow from one trap to another. In this way clusters of conducting paths will be formed throughout the oxide. Once a critical defect density has been reached these clusters will be distributed in such a way that charge can flow from the anode of the gate dielectric to the cathode. At this moment a large discharge will take place, thereby generating the conductive path in the oxide. This is the moment of gate-oxide breakdown.

6 1 Introduction

**Figure 1.2:** Illustration of the formation of a breakdown path as it can be modeled using percolation theory. Three different phases of degradation are shown. Traps are represented as spheres, randomly distributed throughout the oxide. In stage I a few traps have been formed, in stage II clusters of traps can be recognized and in stage III a sufficient number of traps has been formed to have a continuous link of traps between the gate and the substrate. This is the onset of oxide breakdown.

After a breakdown path has been formed it can manifest itself in different ways:

- In hard breakdown, a large gate current increase can be observed. This

type of breakdown is typically found in thick oxide devices and high voltage

stress.

- In soft breakdown [9] a small sudden gate current increase and a sudden gate current noise increase is observed.

- Progressive breakdown [10] is the term used for the non-instantaneous formation of a hard breakdown path.

Hard breakdown has the most disastrous effect on device performance. The effect of progressive breakdown is similar, but only after the degradation has progressed significantly.

#### 1.3.3 NBTI

Negative bias temperature instability (NBTI) is the name for the degradation mechanism mainly seen in pMOSFETs, where a relatively small negative gate voltage can cause device degradation. It cannot be explained using either high energetic charge carriers or degradation mechanisms associated with a tunneling current through the gate-oxide. A similar mechanism can be observed in nMOSFETs, labeled PBTI. NBTI and PBTI combined are referred to as BTI. The first report on NBTI was published in 1966 [11]. The effect has not been considered as an important reliability hazard for a long time. However due to the scaling of the supply voltage and the threshold voltage  $V_{\rm T}$  in CMOS technology, the effect has

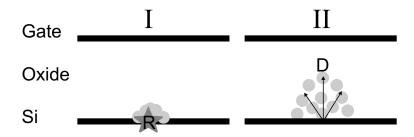

**Figure 1.3:** Schematic illustration of the R-D process for explaining NBTI. In the first phase an electrochemical reaction takes place at the interface between the silicon substrate and the oxide. In this reaction a diffusion species is released. In the second phase this species diffuses into the oxide.

become more and more important since late 1990's [12, 13, 14]. A lot of questions answering the mechanism underlying this effect have since then be answered while other questions still remain open.

It is commonly believed that during NBTI stress both interface traps and positive oxide charge are being formed. Furthermore it is well known that NBTI may recover after removal of the stress signal. This recovery effect may severely affect the obtained degradation rate under NBTI stress if characterization is performed using conventional stress-measure-stress sequences.

The exact nature of the physical mechanism underlying NBTI degradation is still a matter of debate, but the reaction-diffusion (R-D) model is generally believed to appropriately model interface generation under NBTI stress [15, 16, 17, 18]. In this model, illustrated in figure 1.3 it is believed that a two-step process is involved. First a reaction takes place at the Si-SiO $_2$  interface, thereby breaking Si-H bonds, this is followed by diffusion of some hydrogen species into the oxide. Only for very short stress times the reaction rate controls the degradation rate under NBTI stress. For stress times > 0.02-0.03 s [17], the degradation rate becomes limited by the diffusion process.

While it is generally accepted that the nature of interface state degradation can be very well described using the R-D model, controversy still exists on the exact nature of the both the positive oxide charge [17] and the recovery mechanism. Some authors claim that the recovery effect can be completely explained from the R-D framework [15, 16], while others attribute this completely or partly to the detrapping of holes in deep oxide traps [17, 18].

## 1.4 Outline of the thesis

After this introductory chapter, the first topic that is discussed in this thesis is how to perform accurate RF measurements for the purpose of the experiments described later in the thesis. This will be done in chapter 2. Next, in chap-

8 1 Introduction

ter 3, wafer-level MOSFET degradation under RF stress is investigated. Here RF hot carrier, RF NBTI and RF gate-oxide breakdown effects are experimentally investigated and the results are compared to existing models on DC and AC degradation. In chapter 4 a new simulation methodology is presented that allows for the lifetime prediction of RF CMOS PA's. Then, in chapter 5 the use of RF measurement techniques for the reliability characterization of leaky MOS devices will be discussed. The thesis ends with conclusions in chapter 6.

## Chapter 2

## RF MOS measurements

### 2.1 Introduction

Present day state-of-the-art DC measurement equipment is capable of measuring voltage and current signals in the nV respectively fA range [19]. Provided that proper cabling and connections are used, it is relatively easy for a user to obtain these high levels of accuracy. Although highly sophisticated equipment is needed, the user does not need a deep understanding of the underlying measurement principles used, the measurement equipment takes care of this. For RF measurements the situation is a bit more complicated: some aspects of RF measurements require that the user understands the basic measurement principles in order to obtain accurate results. Especially for on-wafer characterization this can be very intricate.

In this chapter some important aspects of RF measurements will be explained, focusing on those measurements relevant for the work described later in this thesis. First in section 2.2 a short overview will be given on how RF measurements differ from DC or AC measurements. Then in section 2.3 it will explained how accurate small-signal characterization of two-port networks can be performed. The work described in section 5.2 of this thesis makes use of these measurement techniques. Finally, in section 2.4 a method is described for generating sinusoidal RF voltage signals with a well-defined amplitude for experiments performed in a one-port on-wafer measurement setup. This method is used for the experiments discussed in chapter 3 and section 5.3 of this thesis.

## 2.2 RF vs. AC/DC measurements

Typical measurement issues that are not encountered in DC and low-frequency measurements, but which are important for RF measurements are the following:

Cables and connections become very lossy when used to transmit high frequency signals.

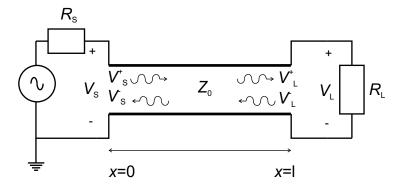

Figure 2.1: Illustration of a transmission line with voltage waves travelling in two directions.  $R_{\rm S}$  is the source series resistance and  $R_{\rm L}$  is the load resistance. In this example  $R_{\rm L} \neq Z_0$ , causing partial reflection of the voltage wave  $V_{\rm L}^+$ .

- Parasitic capacitances and inductances present in the measurement setup can no longer be considered as ideal opens respectively shorts for the high frequencies used.

- The wavelengths of the voltage and current waves of interest are in the same order of magnitude as, or smaller than, the length of the measurement cables.

The first issue can be minimized by making use of dedicated cabling and connections, such as semi-rigid cables and SMA connectors. Furthermore the use of ground-signal-ground probe pad configurations can greatly reduce signal losses for on-wafer RF measurements. Loss free connections are however not available.

The second issue is the cause for large errors in the measured impedance levels of devices if they are not accurately accounted for. Both lossy connections as well as parasitic capacitances and inductances require proper modeling of all parasitic elements in the measurement setup for making accurate measurements. This can be realized by making use of calibration and de-embedding techniques as will be discussed in sections 2.3.2, 2.3.3 and 2.4.

The third issue can best be understood by looking at figure 2.1. In this figure a voltage source is shown with an internal series resistance  $R_{\rm s}$ . It is connected to a transmission line with length l which is terminated with a load resistance  $R_{\rm L}$ .  $Z_0$  represents the characteristic impedance of the transmission line. Throughout this thesis this is always 50  $\Omega$ , the characteristic impedance of the coaxial cables used in the measurements. Voltage signals  $V_{\rm S}$  and  $V_{\rm L}$  are the voltage signals at the source respectively load side. Within the transmission line 4 different travelling voltage waves are indicated.  $V_{\rm S}^+$  and  $V_{\rm S}^-$  represent the voltage waves at the source side, travelling in the positive x-direction respectively negative x-direction respectively negative x-direction respectively negative x-direction respectively negative x-direction. The occurrence of voltage waves travelling in

both directions stems from an impedance mismatch between the characteristic cable impedance  $Z_0$  and the load resistance  $R_{\rm L}$ .

The voltage source causes the voltage wave  $V_{\rm S}^+$ , to propagate along the transmission line in the positive x-direction. This results in  $V_{\rm L}^+$  flowing at the load side of the transmission line. These two voltage waves are related through [20]:

$$V_{\rm L}^{+} = V_{\rm S}^{+} e^{-\gamma l} \tag{2.1}$$

In this expression  $\gamma$  is the complex propagation constant of the transmission line. It comprises of a real part, describing power loss of the travelling signal and an imaginary part describing the phase shift of the signal. In the given example in figure 2.1  $R_{\rm L} \neq Z_0$ ; this is called an impedance mismatch. As a result of this mismatch, part of the travelling voltage wave  $V_{\rm L}^+$  is reflected, causing the voltage wave travelling in the negative x-direction,  $V_{\rm L}^-$ . This wave also propagates along the transmission line resulting in  $V_{\rm S}^-$ .  $V_{\rm S}^-$  and  $V_{\rm L}^-$  are related through [20]:

$$V_{\mathcal{S}}^{-} = V_{\mathcal{L}}^{-} e^{-\gamma l} \tag{2.2}$$

If  $R_{\rm S} \neq Z_0$ , again this voltage wave will be partly reflected;  $V_{\rm S}^+$  is composed of this reflected component and the component directly generated by the source. The two voltage signals  $V_{\rm S}$  and  $V_{\rm L}$  are given by [20]:

$$V_{\rm S} = V_{\rm S}^+ + V_{\rm S}^-$$

$V_{\rm L} = V_{\rm L}^+ + V_{\rm L}^-$  (2.3)

Clearly for a nonzero value of  $\gamma$  these two voltage signals are not equal. Due to the impedance mismatch and the relatively short wavelengths both standing waves and travelling waves occur on the transmission line; this is the cause for this difference. Even if signal loss in the transmission line is negligible (i.e. a zero-valued real part of  $\gamma$ ), the phase shift between the two ends of the transmission line can not be neglected.

This effect gets worse with increasing frequencies as the phase shift is proportional to the frequency of the signal. As a result it is not possible to determine  $V_{\rm L}$  by performing a measurement at the source side of the transmission line. This is what signifies the difficulties in performing RF measurements with respect to DC and AC measurements. In RF measurements the effect of reflections due to impedance mismatch should be carefully taken into account.

An important remark should be made here: the term RF stands for radio frequencies. In this sense it can refer to the frequency of any electromagnetic wave that is used to transmit radio signals. In this thesis use is made of a different definition of RF: it is any frequency high enough for the issues described in this section to appear using measurement cables (transmission lines) with lengths in the order of 1 m. It is common practice to use such a kind of definition; RF measurements are typically considered as being different from AC measurements. The issues described in this section are the problems that make this distinction necessary.

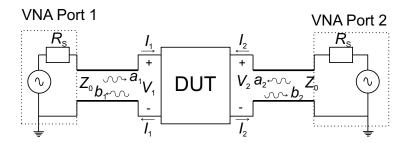

**Figure 2.2:** Two-port *s*-parameter measurement setup.

As a rule of thumb the lower frequency for which the term RF is used is chosen to be 10 MHz in this thesis. This corresponds to a wavelength of 20 m assuming a propagation speed of  $2 \cdot 10^8$  m/s. This is a typical propagation velocity, it is the propagation velocity of TEM waves in coaxial cables that use poly-ethylene as a dielectric material. Frequencies used in this thesis do not exceed the few GHz range, which is still RF in any commonly used definition.

## 2.3 Small signal two-port characterization

The RF measurement issues discussed in the previous section should be taken care of in order to make accurate measurements of devices operating at radio frequencies. In this section small-signal measurements will be discussed. In small signal characterization the measurement setup is assumed to be a linear system. Although typically the device that are characterized are nonlinear by nature, this assumption is allowed if very small amplitudes of the voltage signals are used. In section 2.4.2 a method will be described to determine whether this assumption is allowed or not for a given device and voltage amplitude. Typical voltage amplitudes used in the small signal characterization of MOS devices lie in the order of 100 mV ( $\sim$ -15dBm for  $Z_0=50~\Omega$ ) or lower.

## 2.3.1 s-parameters

Due to the occurrence of both travelling and standing waves, it is not straightforward to characterize a DUT in terms of voltages and currents at RF conditions. Furthermore if one wants to characterize a MOS device, it should be well realized that the DUT has more than two terminals. For this purpose MOS devices are typically characterized in a two-port s parameter measurement setup as illustrated in figure 2.2. Such type of measurements can be performed using a Vector Network Analyzer (VNA). The DUT has two ports, which are connected to the signal ports of the VNA. The VNA is capable of generating well defined travelling waves as well as measure them. The measurement cables and contacts are represented as transmission lines. In the transmission lines travelling waves  $a_1$ ,  $b_1$ ,  $a_2$

and  $b_2$  are indicated. These quantities are typically used when performing VNA measurements. They are defined by [20]:

$$a_{i} = \frac{V_{i}^{+}}{\sqrt{Z_{0}}}$$

$$b_{i} = \frac{V_{i}^{-}}{\sqrt{Z_{0}}}$$

$$(2.4)$$

Using the measured wave quantities, the s-parameters of the DUT can be found. A VNA is capable of obtaining the s-parameters of the DUT. The s-parameters are defined by [21]:

$$s_{11} = \frac{b_1}{a_1}|_{a_2=0}$$

$$s_{12} = \frac{b_1}{a_2}|_{a_1=0}$$

$$s_{21} = \frac{b_2}{a_1}|_{a_2=0}$$

$$s_{22} = \frac{b_2}{a_2}|_{a_1=0}$$

(2.5)

These four s-parameters completely describe the two-port behavior of the DUT. They can easily be transformed into other types of two-port parameters, (e.g. z-or y-parameters), describing the DUT in terms of voltages and currents. So, in short, by measuring the wave quantities  $a_1$ ,  $a_2$ ,  $b_1$  and  $b_2$  and deriving the s-parameters as in 2.5, VNA measurements provide the complete small-signal two-port behavior of a DUT in terms of voltages and currents. When performed over a broad frequency range, these measurements can be used to determine important device parameters such as the cut-off frequency  $f_T$  and the maximum frequency of oscillation  $f_{\text{max}}$ . They can also be used for obtaining C-V curves as will be explained in section 5.2.

#### 2.3.2 Calibration

A VNA is capable of measuring s-parameters; it cannot, however, measure the power waves directly at the DUT, but only at the VNA side of the transmission lines. In order to make s-parameter measurement at the DUT possible, the measurement setup needs to be calibrated first. The calibration process takes into account any error due to nonzero propagation constants of the transmission lines as well as errors introduced by the VNA itself. Several calibration procedures have been developed, these will not all be discussed here; a good explanation on different calibration procedures can be found in [22]. Any commercially available VNA provides the necessary tools for performing calibration for s-parameter measurements.

The key idea of calibration is to characterize the errors in the measurement setup by replacing the DUT in figure 2.2 with well characterized calibration standards. A commonly used calibration procedure for two-port networks is SHORT-OPEN-LOAD-THROUGH (SOLT) calibration. This is the calibration procedure used in this thesis when two-port s-parameter measurements are performed. In SOLT calibration the calibration standards consisting of a SHORT, OPEN and LOAD standard are consecutively connected at both ports of the DUT followed by a THROUGH standard that links both ports of the DUT. The LOAD standard is typically a 50  $\Omega$  resistive structure, thereby providing perfect matching to  $Z_0$ . For all these connections the a and b waves are measured at the VNA side of the transmission lines in figure 2.2. In this way the error terms present in the measurement setup can be found. This type of calibration can be performed on-wafer, thereby providing accurate s-parameter measurements at the tip of the probe needles.

The one-port equivalent of SOLT calibration is SOL calibration. It only differs form SOLT calibration in the sense that no measurements are made at port 2, hence the THROUGH connection cannot be used. SOL calibration consists of three measurements, a SHORT, OPEN, and a LOAD measurement. For this purpose the measurement setup is typically described using a three-term error model [22]. This model is a simplification of a four-term error model [22], but it is adequate for calibration a measurement for obtaining the reflection coefficient at the DUT,  $\Gamma_{\rm DUT}$ . As with SOLT, SOL calibration provides no information on the absolute values of the power and voltage waves flowing in the measurement setup, only the ratio between the incoming and reflected waves at the DUT is known. In section 2.4 it will be explained how the use of a 4-term error model provides the possibility of also obtaining these absolute levels.

## 2.3.3 De-embedding

Even though the measurement setup can be calibrated to the tip of the probe needles for on-wafer measurements, some errors still remain unaccounted for. These can be attributed to the bond pads and interconnect lines, that connect the probe needles to the intrinsic DUT. The bond pads can cause a parasitic capacitance parallel to the DUT. Typical values of this bond pad capacitance are in the range of 100 fF. This results in a parasitic admittance of  $\sim j.0.6$  mS for a measurement at 1 GHz. The interconnect lines cause a parasitic series line inductance, typical values of this inductance are in the range of 100 pH. This coincides with a series parasitic impedance of  $\sim j.0.6$   $\Omega$  for a 1 GHz signal.

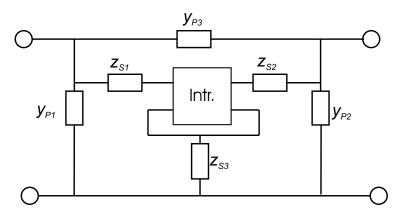

These parasitic impedances and admittances can seriously affect the accuracy of the obtained measurement results, even after calibration to the tip of the probe needle. Especially for frequencies exceeding 1 GHz this becomes more and more important. These test structure parasitics must therefore be accounted for as well. The technique for correcting for these parasitics is called de-embedding. For frequencies up to  $\sim\!20$  GHz, the most commonly used de-embedding method is OPEN-SHORT de-embedding.

OPEN-SHORT de-embedding can be understood by modeling the test structure parasitics as done in figure 2.3 [23]. The parasitic admittances originating

**Figure 2.3:** Two-port model of a test structure with parasitics as it is used in OPEN-SHORT de-embedding.

**Figure 2.4:** Layout of test structures for OPEN-SHORT de-embedding in a ground-signal-ground configuration. From left to right: the actual DUT, the OPEN de-embedding structure and the SHORT de-embedding structure.

from the bond pad capacitances are represented by  $y_{\rm P1}$ ,  $y_{\rm P2}$  and  $y_{\rm P3}$ . The parasitic impedances originating from the line impedances are represented by  $z_{\rm S1}$ ,  $z_{\rm S2}$  and  $z_{\rm S3}$ . The goal of de-embedding is to account for these parasitics so that the two-port behavior of the intrinsic DUT can be found.

In OPEN-SHORT de-embedding the two-port parameters of the three structures of figure 2.4 are measured. The OPEN and SHORT de-embedding structures are different from the OPEN and SHORT calibration structures used in SOLT calibration. The de-embedding structures are two-port structures whereas the OPEN and SHORT calibration structures are one-port structures. Furthermore de-embedding structures are not ideal structures as opposed to calibration structures. The de-embedding structures have the same parasitics as the DUT structure. De-embedding measurements are performed on-wafer, while calibration measurements are performed on a separate calibration substrate.

If the two-port parameters of the three structures of figure 2.4 are determined

it can be derived that [23]:

$$\overline{y_{\rm I}} = \left( (\overline{y_{\rm D}} - \overline{y_{\rm O}})^{-1} - (\overline{y_{\rm S}} - \overline{y_{\rm O}})^{-1} \right)^{-1} \tag{2.6}$$

In this expression  $\overline{y_{\rm I}}$ ,  $\overline{y_{\rm D}}$ ,  $\overline{y_{\rm O}}$  and  $\overline{y_{\rm S}}$  represent two-by-two y-parameter of the intrinsic device, the DUT, the OPEN structure respectively SHORT de-embedding structure. Using this expression the two-port behavior of the intrinsic device can be found. Expression 2.6 only provides accurate results as long as  $\overline{y_{\rm I}}$  is significant compared to  $\overline{y_{\rm O}}$  and  $\overline{y_{\rm S}}$ , due to limitations in the resolution of the measurement setup. This can be assured by careful design of the test structure.

De-embedding is not always automated in VNA equipment. Typically VNA measurements are performed on the DUT followed by the two de-embedding structures. Working out equation 2.6 is part of the data analysis performed by the user. In the work described in this thesis use is made of a MATLAB routine for this purpose.

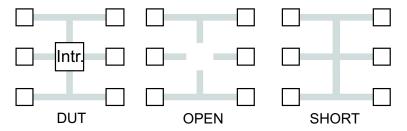

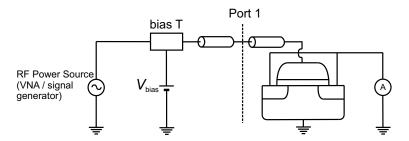

## 2.4 Linear one-port RF voltage generation

Whereas measurements in terms of small signal s-parameters are adequate for characterizing a vast amount of device parameters, this may not always be applicable. In chapter 3 and section 5.3 experiments will be discussed that require well-defined voltage signals with frequencies up to 4 GHz. Assessing voltage waveforms at the DUT is not straightforward, especially for on-wafer measurements. Nowadays commercially available equipment exists that allows for obtaining the time-domain voltage and current waveforms on nonlinear devices [24]. The experiments discussed in this thesis, however, do not require all the complexity involved in such equipment: only sinusoidal voltage signals are considered, where its phase is irrelevant in its analysis. This makes large-signal measurement equipment overly complex- and expensive- for the purpose of the experiments described in this thesis. In this section the methodology will be described that is used throughout this thesis for generating sinusoidal voltage signals with a well-defined amplitude in a one-port on-wafer experiment.

As only purely sinusoidal voltage signals are used, a linear VNA is suitable for generating the required signal for the experiments of chapter 3 and section 5.3. Since a VNA is not designed for performing these experiments, they typically do not provide information on the voltage signals during measurements. Based on well-accepted models it is, however, possible, to obtain this information without the need for any additional complexity to the measurement setup.

## 2.4.1 Setting the amplitude

For generating sinusoidal voltage signals, use is made from the measurement setup shown in figure 2.5. In this figure a VNA is represented as consisting of a power source, two directional couplers, local oscillator (LO) circuits and A/D and IF

**Figure 2.5:** Schematic drawing of the setup used for the RF voltage generation procedure used in this thesis. A VNA is used to generate large amplitude sinusoidal voltage signals at the DUT. The DUT is laid out in a ground-signal-ground configuration and is connected on-wafer. The VNA is controlled via Labview software on a PC that is connected through an IEEE 488 bus.

processing circuitry. It is a very simple description of a VNA, but it is suitable for understanding the voltage generation procedure discussed in this section. The VNA is connected to a PC with Labview software, through an IEEE 488 bus. An externally generated DC voltage  $V_{\rm bias}$  is superimposed on the RF signal by means of the bias T.

The VNA in this setup is connected in a one-port arrangement, the VNA operates in continuous wave mode. The power source generates  $a_s$ ; this wave will flow towards the DUT and it will be partly reflected, causing a wave flowing in the opposite direction. With the use of the two directional couplers it is possible to measure both the a and b waves separately. The coupled signal is multiplied with an LO signal and after IF processing and A/D conversion the complex measured waves  $a_m$  and  $b_m$  are known. These variables differ from the actual waves at the DUT; calibration is needed to find the amplitude of the voltage signal at the DUT by recording  $a_m$  and  $b_m$ .

The amplitude and phase of  $a_{\rm m}$  and  $b_{\rm m}$  are read by the PC, and from these the peak-to-peak value of the voltage signal applied at the DUT,  $V_{\rm DUT,pp}$  is determined in a Labview routine. Setting the desired value of  $V_{\rm DUT,pp}$  is realized by increasing  $a_{\rm s}$  in small steps and monitoring  $V_{\rm DUT,pp}$  until its desired value is reached.

In order to determine  $V_{\rm DUT,pp}$  from the obtained complex parameters  $a_{\rm m}$  and  $b_{\rm m}$  the measurement setup needs to be calibrated. As this setup is custom built,

**Figure 2.6:** Signal flow graph depicting the 7 error terms of the setup of figure 2.5.

only for the purpose of the measurements discussed in this thesis, the necessary equations for the calibrations must be derived; calibration software inside the VNA used for the experiments discussed in this thesis does not provide the appropriate control over  $V_{\rm DUT,pp}$ .

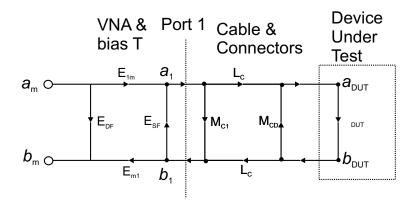

Similar to the calibration procedures discussed in section 2.3.2 a VNA can be modeled in a Signal Flow Graph for the purpose of characterizing the error terms. The SFG used is shown in figure 2.6. This SFG has 7 error terms. It is a combination of a four-term error model and a three-term error model. These error models are commonly used models in one-port calibration of VNA's [22]. The four-term error model describes the behavior of the VNA in combination with the used bias Tees and some cabling. The three-term error model consists only of cabling, connectors and the probes for on-wafer characterization. This cable & connector network is a reciprocal network, reflected by the two equal  $L_{\rm C}$  terms shown in figure 2.6.

The reason for splitting the measurement setup into a "VNA & bias Tee" and a "Cable & Connectors" network stems from the fact that an absolute power measurement is needed in order to calculate  $V_{\rm DUT,pp}$  from  $a_{\rm m}$  and  $b_{\rm m}$ , as will be made clear below. This power meter measurement cannot be performed on-wafer, therefore this is done at Port 1. Making use of the reciprocity of the "Cable & Connector" network this allows for determining the absolute value of the waves at the DUT, in an on-wafer experiment.

The error terms are determined by making use of calibration standards. As the SFG of figure 2.6 has 7 error terms, 7 well-chosen calibration measurements are needed for characterizing the complete measurement setup. The error terms can be dependent on both frequency and power, therefore these calibration measurements are performed over a broad range of frequencies and power levels. The result of the calibration procedure is a large database containing information on the 7 error terms for all frequencies and power levels used in the experiments,

stored on the PC. Using this database,  $V_{\rm DUT,pp}$  can be calculated from any  $a_{\rm m}$ ,  $b_{\rm m}$  combination at any given frequency or power level. This calculation is done within a Labview routine.

The calibration measurements start with a SHORT, OPEN and LOAD measurement at Port 1. From these three measurements error terms  $E_{\rm DF}$ ,  $E_{\rm SF}$  and  $E_{\rm 1m} \cdot E_{\rm m1}$  can be found. The next step is to measure the absolute power level at Port 1 using an external power meter for all frequencies and power levels of interest. In the work described in this thesis an HP 437B power meter is used for this purpose; it is also connected to the PC, through an IEEE 488 bus. Using this power measurement a value for  $|E_{\rm 1m}|$  can be found. Next the "Cable & Connector" network is connected to Port 1. The calibration procedure completes with a SHORT, OPEN and a LOAD measurement using standards on a calibration substrate for on-wafer calibration. These three measurements provide values for  $M_{\rm C1}$ ,  $M_{\rm CD}$  and  $L_{\rm C}$ .

The equations underlying this calibration procedure follow straightforwardly from the SFG of figure 2.6. They are worked out in appendix A, together with the equations needed to relate  $V_{\rm DUT,pp}$  to  $a_{\rm m}$  and  $b_{\rm m}$ .

## 2.4.2 Verifying linearity

The calibration technique discussed above is only suitable if the voltage signal at the DUT is purely sinusoidal; this can only be realized using a DUT with linear input impedance. The input impedance of the devices discussed in chapter 3 and section 5.3 are, however, not perfectly linear. This can be overcome by choosing a voltage amplitude sufficiently low, so that the device is operating in small-signal regime. Choosing an amplitude too low, on the other hand, counteracts the purpose of the experiments of chapter 3 and section 5.3. In these experiments, the amplitude is necessarily chosen as large as possible. Setting up an experiment that fulfills both the demand of linearity and of having an amplitude sufficiently large for making the experiments relevant, is a crucial step in the methodology used in this thesis for generating RF voltage signals.

Various methods exist that allow for checking for nonlinear behavior of devices [25]. These methods can be used to determine the maximum voltage amplitude of an RF signal that can be superimposed on a DC voltage  $V_{\rm bias}$  for which linearity can be guaranteed. For the experiments in chapter 3 however, it is needed to know the maximum voltage amplitude that can be generated for which linearity can be guaranteed, with a fixed value of the maximum voltage level,  $V_{\rm max}$ . The existing methods could be used for this purpose, by measuring the maximum tolerable power level as a function of  $V_{\rm bias}$ . Using the calibration procedure discussed in the previous section, the maximum tolerable voltage amplitudes could then be calculated from the obtained power levels. This would result in a large database from which the information of interest (i.e. the largest tolerable voltage amplitude with a given  $V_{\rm max}$ ) could be extracted. For the work described in this thesis a different approach was adopted in which considerably less measurements are required for obtaining the information of interest.

The key idea of the applied method is to calculate the voltage signal at the DUT on the basis of a measured small-signal input impedance of the DUT and check whether the resulting waveform is indeed sinusoidal. For this purpose the input impedance of the DUT is measured as a function of  $V_{\rm bias}$  using a VNA connected in one-port setup with the power level set to -15 dBm. The voltage waveform is determined by solving transmission line equations within a MATLAB routine. The small-signal characterization is performed on one device, the actual experiments as discussed in chapter 3 and section 5.3 are performed on the same type of device, but on different dies on the same wafer.

In order to perform the necessary calculations, first the appropriate equations will be derived. When an RF power signal is applied to a DUT, a part of the signal can be reflected, due to an impedance mismatch between the characteristic impedance of the cable and the input impedance of the DUT. The resulting voltage waveform at DUT level is a direct function of this amount of mismatch. The reflection coefficient, and hence the resulting voltage waveform at the DUT, can be determined by solving transmission line equations. These equations are based on the fact that the current flowing in the measurement cable must equal the current flowing into the DUT. When dealing with a linear input impedance of the DUT it is given by [20]:

$$\frac{V^{+} - V^{-}}{Z_{0}} = \frac{V_{\text{DUT}}}{Z_{\text{DUT}}} \tag{2.7}$$

In this expression  $V^+$  and  $V^-$  represent the incoming respectively reflected voltage wave, as defined in [20] and  $V_{\rm DUT}$  is the resulting voltage signal at the DUT. All three voltage signals in this expression are represented in a complex phasor notation. In this expression perfect linear behavior of the DUT is assumed. This equation can be solved by realizing that [20]:

$$V_{\rm DUT} = V^+ + V^- \tag{2.8}$$

The idea is now that equation 2.7 is solved using the actual measured input impedance of the DUT and verify whether the outcome indeed represents a perfectly sinusoidal signal (i.e. higher harmonics are negligible). If this is true, the assumption of linear behavior is allowed, thereby proving the validity of equation 2.7 and that of the resulting calculated waveform.

Expressions are needed for the following parameters:  $V^+$ ,  $Z_0$  and  $Z_{\rm DUT}$ .  $V^-$  and  $V_{\rm DUT}$  are solutions to equation 2.7.  $V^+$  is the incoming voltage wave, its amplitude should be chosen such that it leads to the desired value of  $V_{\rm DUT}$ . In practice this means that the solution to equation 2.7 will be obtained with various values of  $V^+$ ; only the value of  $V^+$  that leads to the desired value of  $V_{\rm DUT}$  is considered.

More difficult is choosing the appropriate value of  $Z_{\rm DUT}$ , it can be a complex variable, that is dependent on  $V_{\rm DUT}$ . The latter is typical for the devices used in this thesis, consider, e.g., the voltage dependent gate capacitance of a MOSFET structure. Due to the fact that  $Z_{\rm DUT}$  can be voltage dependent, equation 2.7 cannot be solved in the frequency domain, thereby prohibiting the use of complex

phasor notations. Another way of describing this equation is needed. The equation is rewritten in time-domain, with the imaginary component of  $Z_{\rm DUT}$  described in a differential equation.

For the devices used in this thesis it will turn out that the imaginary part of  $Z_{\rm DUT}$  is either negligible or negative, under the measurement conditions of interest. This corresponds to a capacitive input. When assuming sinusoidal steady-state and a negative imaginary component of  $Z_{\rm DUT}$ , it can be derived that equation 2.7 can be written in time-domain as:

$$\frac{V^{+}(t) - V^{-}(t)}{Z_{0}} = V_{\text{DUT}}(t) \left[ G_{\text{DUT}}(V_{\text{DUT}}(t)) + \frac{dC_{\text{DUT}}(V_{\text{DUT}}(t))}{dt} \right] + \frac{dV_{\text{DUT}}(t)}{dt} C_{\text{DUT}}(V_{\text{DUT}}(t))$$

(2.9)

In this expression all voltage signals are expressed in time domain.  $G_{\rm DUT}(V_{\rm DUT}(t))$  and  $C_{\rm DUT}(V_{\rm DUT}(t))$  are the input admittance respectively input capacitance of the DUT at time t, if the input voltage is equal to  $V_{\rm DUT}(t)$ . The relation between parameters  $G_{\rm DUT}$ ,  $C_{\rm DUT}$  and  $V_{\rm DUT}$  can be obtained from the measured  $\Gamma_{\rm i}$ , obtained in a one-port setup and after SOL calibration of the VNA. This should be done over the entire voltage and frequency range of interest. Having a value of  $\Gamma_{\rm DUT}$  for the appropriate value of  $V_{\rm DUT}$  and the correct frequency, parameter  $z_{\rm in}$  can be found from:

$$z_{\rm in}(V_{\rm DUT}) = Z_0 \frac{1 + \Gamma_{\rm DUT}(V_{\rm DUT})}{1 - \Gamma_{\rm DUT}(V_{\rm DUT})}$$

(2.10)

Now if  $V_{\text{DUT}}(t)$  is known,  $z_{\text{in}}(V_{\text{DUT}}(t))$  can be found from the measured data and  $G_{\text{DUT}}(V_{\text{DUT}}(t))$  and  $C_{\text{DUT}}(V_{\text{DUT}}(t))$  can be derived using:

$$G_{\text{DUT}}(V_{\text{DUT}}(t)) = \Re\left(\frac{1}{z_{\text{in}}(V_{\text{DUT}}(t))}\right)$$

$$C_{\text{DUT}}(V_{\text{DUT}}(t)) = \frac{1}{2\pi f} \Im\left(\frac{1}{z_{\text{in}}(V_{\text{DUT}}(t))}\right)$$

(2.11)

The solution to equation 2.9 can now be found by making use of the measured values of  $G_{\text{DUT}}$  and  $G_{\text{DUT}}$  as a function of  $V_{\text{DUT}}$ .

No general analytical solution can be found for equation 2.9 and therefore a numerical solution technique is used. This means that equation 2.9 is solved in discrete time domain. For this purpose voltage signals  $V^+(t)$ ,  $V^-(t)$  and  $V_{\rm DUT}(t)$  are discretized in 200 time steps per period. Now for every time step an optimization algorithm embedded in a MATLAB routine finds the solution to equation 2.9. The time derivatives in equation 2.9 are replaced by their discrete-time equivalent for this purpose. In this way the time domain representation of  $V_{\rm DUT}(t)$  can be found. The peak-peak voltage of the sinusoidal voltage signal  $V^+(t)$ ,  $V_{\rm pp}^+$ , can be tuned to result in the desired amplitude of  $V_{\rm DUT}(t)$  by repeatedly performing this solution procedure for different values of  $V_{\rm pp}^+$ .

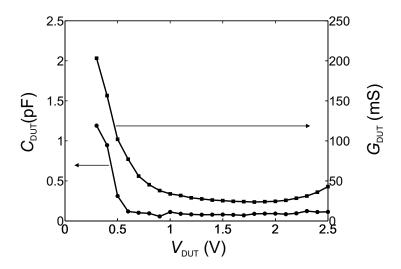

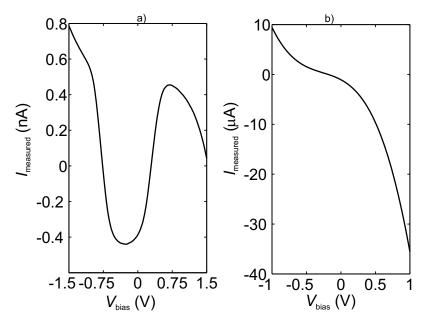

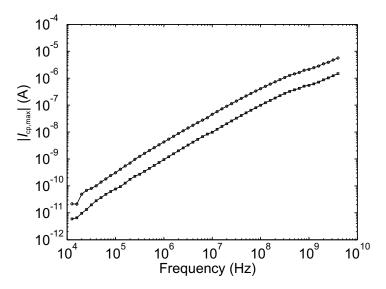

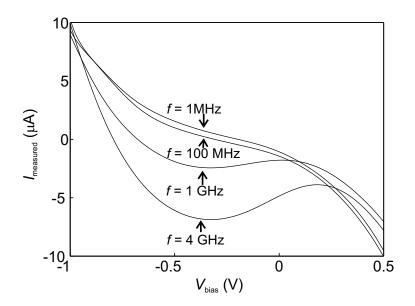

**Figure 2.7:** Example of the DUT impedance measured as a function of  $V_{\rm DUT}$ . Small-signal s-parameters were performed in a one-port measurement setup and  $G_{\rm DUT}$  and  $C_{\rm DUT}$  were extracted using the equations in 2.11 at a frequency of 3.2 GHz. The DUT is an nMOSFET connected at its drain terminal with the gate voltage set to 1.5 V. For voltages above  $\sim$  1 V the nMOSFET operates in the saturation regime. This DUT is useful for performing RF hot carrier experiments as will be explained in section 3.2.

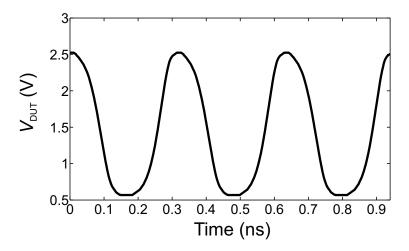

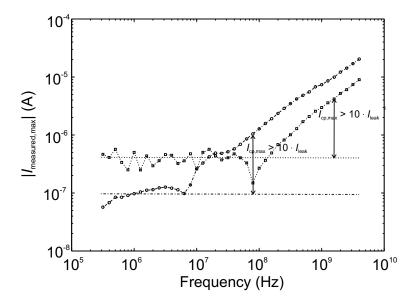

The resulting waveforms indicate whether sinusoidal voltage signals at the input of the DUT can be guaranteed, for the desired amplitude of  $V_{\rm DUT}(t)$  and the measured values of  $G_{\rm DUT}(V_{\rm DUT})$  and  $C_{\rm DUT}(V_{\rm DUT})$ . In figure 2.7 and 2.8 the importance of this analysis is illustrated. Figure 2.7 shows an example of the DUT impedance measured as a function of  $V_{\rm DUT}$ . The DUT is an actually used DUT in this thesis; it is used for RF hot carrier experiments. The DUT consists of an nMOSFET, connected at the drain side, with the gate voltage set to 1.5 V. This means that the observed  $G_{\rm DUT}$  and  $C_{\rm DUT}$  are the conductance and capacitance are the impedance seen at the drain, as a function of drain voltage. For voltage levels above  $\sim 1$  V, the nMOSFET operates in the saturation regime; at lower gate voltages the DUT impedance has a stronger dependency on the applied voltage  $V_{\rm DUT}$ .

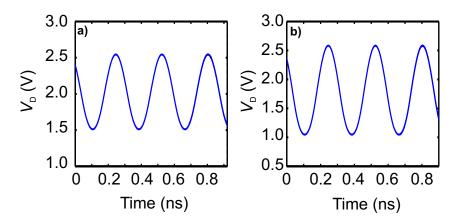

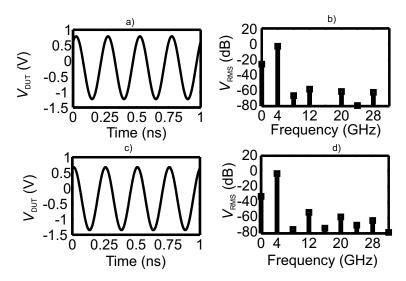

The signal integrity analysis is applied to this DUT at a frequency of 3.2 GHz, the frequency for which this DUT is used in the RF hot carrier experiment. The DC offset voltage was set to 1.25 V and the waveform was calculated for an incoming voltage wave with an amplitude of 1.77 V (16.5 dBm). The resulting waveform is shown in figure 2.8. Clearly the resulting waveform suffers from harmonic distortion. It is not a sinus and therefore the amplitude should be reduced in order to use the DUT in an RF hot carrier experiment. In section 3.2

2.5 Conclusions 23

**Figure 2.8:** Calculated waveform at 3.2 GHz using the measured input impedance of figure 2.7. In this example the amplitude of the DUT voltage is chosen too high for obtaining a sinusoidal voltage signal at the DUT. The amplitude should be reduced in order to guarantee linearity. In figure 3.3 b) the waveform as used in RF hot carrier experiments on this device is shown.

it is explained which voltage level is chosen for this DUT, the result can be seen in figure 3.3 b).

The signal integrity analysis discussed here was performed prior to any measurement discussed in this thesis. If the resulting waveform indicated that non-linearities were not negligible, different measurement conditions were chosen (e.g. lower amplitudes of  $V_{\rm DUT}(t)$ ), such that this could be guaranteed. The effect of the introduction of higher harmonics due to a nonlinear input impedance is one of the causes that limits the use of higher frequencies than the ones discussed in chapter 3 and section 5.3, i.e. up to 4 GHz. It should be noted however that the measurements discussed in these chapters are already performed at frequencies far beyond conventional measurements and suffice to answer the research questions on RF reliability in CMOS for contemporary wireless applications.

## 2.5 Conclusions

RF measurements differ from AC and DC measurements in the fact that voltage and current signals occurring at the DUT may significantly differ from those at the source. In this chapter an overview is given of the RF measurement techniques used for the experiments discussed later in this thesis. These techniques include widely used small-signal characterization tools as well as a methodology for generating well-defined large-amplitude voltage signals for on-wafer experiments.

Small-signal s-parameter characterization is a well-established technique. Ac-

companied with calibration and de-embedding it provides a very accurate measurement of a two-port network connected on-wafer. Various calibration and de-embedding techniques exist, but for the purpose of the experiments discussed in this thesis it suffices to make use of SOLT calibration and OPEN-SHORT de-embedding.

In this chapter the voltage generation procedure as used for the RF stress and RF charge pumping measurements, discussed later in this thesis, is presented. The key idea of the technique is to generate sinusoidal voltage signals with a voltage amplitude as large as possible, but low enough for nonlinearities to be negligible. Sinusoidal voltage signals are useful for both RF stress and RF charge pumping measurements. A consequence of using only sinusoidal signals, is that it suffices to use only a VNA in the measurement setup, thereby allowing to omit the use of complex large-signal measurement equipment for determining the exact voltage waveform at DUT level. This methodology is very effective for performing the experiments discussed later in this thesis.

## Chapter 3

# MOSFET degradation under RF stress

## 3.1 Introduction

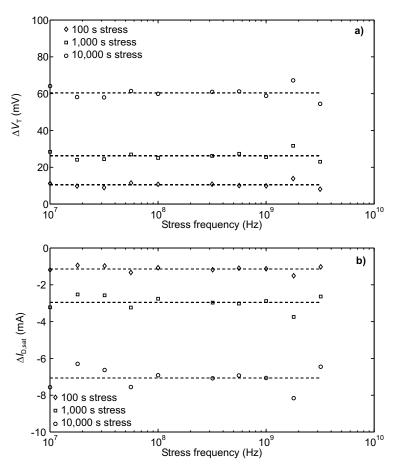

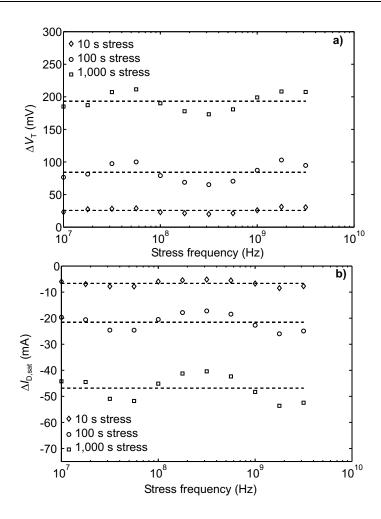

A key aspect of reliability engineering is getting a good understanding of physical mechanisms underlying device failure. For MOSFET degradation mechanisms this issue has been widely discussed for the DC case and various models have been developed for explaining degradation rates of the devices under different biasing conditions. These models can be used for making lifetime predictions of different circuits. For use in RF circuits it is of crucial importance to understand how applicable these DC models are under RF conditions. Some authors have compared DC stress conditions to AC conditions (see e.g. [26]), but stress under RF conditions is only marginally addressed in literature. One of the main reasons for this is that it is not straightforward to perform accurate reliability experiments at frequencies exceeding 10 MHz. Some authors did measure device degradation when operated in RF circuits [27, 28], but an accurate comparison with low frequency results could not be made. To do this, experimental results are needed that reveal whether or not degradation mechanisms are frequency dependent between the MHz and the GHz range.

Given the fact that all models describing the degradation mechanisms discussed in section 1.3, are all either voltage or field based, the generation of well-defined RF voltage signals is a critical issue. In this chapter the frequency response of the degradation mechanisms discussed in section 1.3 will be investigated using the voltage generation procedure as explained in section 2.4. This will be preceded, for every degradation mechanism, by a short overview on what is known from literature concerning the applicability of DC models for AC stress conditions. The combination of these DC to AC and AC to RF comparisons can be used to shed insight on the applicability of DC models for RF stress conditions. In section 3.2 this will be done for the hot carrier effect. This is followed by the

NBTI effect in section 3.3 and gate-oxide breakdown in section 3.4.

## 3.2 RF hot carrier degradation

#### 3.2.1 DC model

As explained in section 1.3, the hot carrier effect is the degradation effect caused by high energetic charge carriers flowing in the channel of a MOSFET. This effect has been widely discussed in literature (see e.g. [29, 30, 31, 32, 33]). The effect can be observed in both nMOSFETs and pMOSFETs; hot carrier degradation in nMOSFETs however has received much more attention in literature than pMOSFET degradation. This is due to the fact that the effect of nMOSFET hot carrier degradation on digital circuit performance is more severe than pMOSFET hot carrier degradation. Similarly, when considering hot carrier degradation in RF circuits, investigating nMOSFET degradation is much more relevant than pMOSFET degradation, as will also be explained in subsection 3.2.2. Therefore in this section only hot carrier degradation in nMOSFETs will be considered.

From literature it is known that the hot carrier degradation rate is dependent on both the drain and the gate voltage. An increase in drain voltage leads to a higher lateral electric field in the channel, thereby generating more hot carriers. With a gate voltage biased at maximum degradation rate conditions, the hot carrier lifetime is usually related to the drain voltage as in [29]:

$$\tau_{\rm HC} = A \cdot e^{\frac{B}{V_{\rm D}}} \tag{3.1}$$

In this expression  $\tau_{\rm HC}$  is the hot carrier lifetime of the device. It can be defined as the time at which any device parameter has degraded by a given quantity (such as a 50 mV shift in the threshold voltage  $V_{\rm T}$ ) or fraction (typically 10%). Parameters A and B are dependent on the device parameter it concerns, the technology used and the stress conditions.  $V_{\rm D}$  is the applied drain voltage level.

For a given drain voltage level, the rate of hot carrier degradation is strongly dependent on the gate voltage level applied to the device. For devices with channel lengths  $> 0.25~\mu\mathrm{m}$  three different regions of gate bias voltage can be distinguished under which hot carrier degradation is most severe. These three regions are listed in table 3.1 for nMOSFETs [32]. In this table it can be seen that hole trapping and interface state generation dominate at low gate voltages and electron trapping at high gate voltage levels. At medium gate voltage levels, the generation of interface states is dominant. For such long channel length devices, the maximum degradation rate was found to occur at medium gate voltage levels. This condition coincides with the condition for maximum substrate current. For this reason, the worst-case hot carrier lifetime of conventional nMOSFETs was typically characterized at maximum substrate current condition.

With the newer generations of MOSFETs, with channel lengths below 0.25  $\mu$ m the gate voltage for maximum degradation rate was found to be shifted to high gate voltage levels ( $V_G \cong V_D$ ), experimentally demonstrated in [34].

| פי | g channel devices [32].               |                            |  |  |  |  |  |  |  |

|----|---------------------------------------|----------------------------|--|--|--|--|--|--|--|

|    | $V_{ m G}$ range                      | Degradation mechanism      |  |  |  |  |  |  |  |

| ĺ  | $V_{\rm G}\cong V_{ m T}$             | Interface state generation |  |  |  |  |  |  |  |

|    |                                       | Hole trapping              |  |  |  |  |  |  |  |

|    | $V_{\rm G} \cong \frac{V_{\rm D}}{2}$ | Interface state generation |  |  |  |  |  |  |  |

|    | $V_{ m G}\cong 	ilde{V_{ m D}}$       | Electron trapping          |  |  |  |  |  |  |  |

**Table 3.1:** Dominant nMOSFET hot carrier degradation mechanisms at different gate bias for long channel devices [32].

The occurrence of different hot carrier degradation mechanisms at different gate voltage signals makes the lifetime prediction of AC and RF circuits challenging. For DC stress signals it is obvious which hot carrier degradation mechanism is dominant for a given MOSFET. For AC and RF circuits on the other hand, the total hot carrier degradation may consist of the contribution of different hot carrier degradation mechanisms. This must carefully be taken into account.

#### 3.2.2 AC effects

Early reports on AC hot carrier degradation reported on an enhanced AC effect with increasing frequency, which was later explained by Bellens et al. as a measurement artifact [35]. They showed that the self inductance of the wiring in the measurement cables can cause large voltage overshoots. This conclusion made the interpretation of earlier reported results questionable and it signifies the importance of generating well-defined voltage levels for performing AC reliability experiments. For AC hot carrier experiments up to 10 MHz this signal distortion due the cable inductance can be overcome by adding a large parallel capacitor to the DUT at the drain side [35]. For higher frequencies additional effects such as signal distortion due to impedance mismatch come forward, as explained in chapter 2.

Since in digital circuitry clock frequencies exceeding 100 MHz have been readily available in the early 1990's, the desire for evaluating device degradation under AC stress signals with frequencies far beyond 10 MHz has emerged years before CMOS was introduced into RF circuits. In order to solve the measurement issues that arise at such high frequencies, self stressing devices were introduced [36, 37, 38, 39]. These self-stressing structures consist of oscillator and inverter circuits in which high-frequency stressing signals are generated on-chip. Using these structures, hot carrier experiments with inverter switching frequencies up to 369 MHz were already reported as early as 1994 [39]. None of these experiments revealed any unexpected effects occurring during AC stress.

When comparing AC hot carrier degradation to DC degradation Mistry et al. showed that use can be made of quasi-static assumptions [40]. Care should be taken that the contributions of all hot carrier degradation mechanisms as depicted in table 3.1 are taken into account. This may be done using a Matthiesen-like

formula [40]:

$$\frac{1}{\tau_{\rm AC}} = \frac{1}{\tau_{N_{\rm ir}}} + \frac{1}{\tau_{\rm e}} + \frac{1}{\tau_{\rm h}} \tag{3.2}$$

In this expression  $\tau_{AC}$  is the actual device lifetime under AC stress conditions,  $\tau_{N_{\rm it}}$  is the device lifetime taking into account only the generation of interface states,  $\tau_{\rm e}$ , device lifetime based on electron trapping and  $\tau_{\rm h}$ , lifetime concerning only hole trapping.

With reducing supply voltages in CMOS technologies since the late 1990's, hot carrier degradation has become less of an issue for digital circuitry. Therefore the need for investigating AC hot carrier degradation at even higher frequencies became less evident. In RF circuits, on the other hand, voltage signals exceeding nominal supply voltage are no exception, especially in PA's. Therefore in RF circuits, the AC hot carrier effect may become a very important degradation mechanism if this is not accurately taken care of. This was acknowledged by Presti at al. in [28], where hot carrier degradation was measured for an nMOSFET operating at 1.9 GHz. Their approach however prevented an accurate comparison with lower frequency signals, thereby not shedding insight on any frequency dependence of the hot carrier effect.

When designing PA's in CMOS technology, it is most desirable to use nMOS-FETs as the power driving transistors. This is because of their superior current -and hence power- driving capabilities over pMOSFETs. One of the main issues with RF PA design is guaranteeing a sufficiently high output power while keeping the drain voltage at an acceptably low level. This may not always be feasible with voltage signals below nominal supply voltage. It is for this reason that a proper investigation of hot carrier degradation under RF conditions is very relevant. As typically no pMOSFETs are used for this purpose, the work in this section only focuses on RF hot carrier degradation in nMOSFETs.

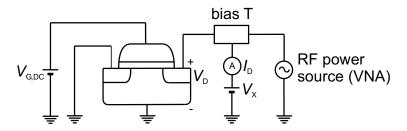

When performing RF hot carrier experiments it is important to realize that the highest voltage signals occur at the drain side of the devices, if the devices are used in PA's. It is therefore most relevant to investigate RF hot carrier degradation with an AC drain voltage. Such a kind of stress is used in this section with the gate voltage kept constant. This is different from earlier AC hot carrier experiments where the behavior of digital circuits was mimicked. For these experiments an AC gate voltage with constant drain voltage was more appropriate for describing actual circuit behavior.

In [41] a theoretical analysis is given of RF to DC lifetime ratios under such stressing conditions. The model assumes quasi-static behavior while it has not been experimentally verified. This will be done in this section for sinusoidal drain voltage signals by investigating the frequency dependence from the MHz towards the GHz range, and knowing that quasi-static assumptions are allowed in the MHz range, as discussed above.

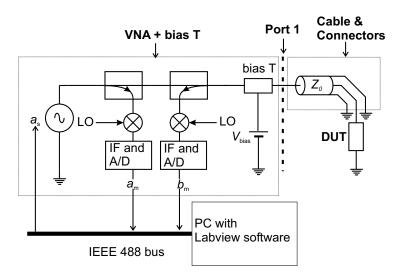

Figure 3.1: Schematic drawing of the RF hot carrier measurement setup.

## 3.2.3 Measurement setup

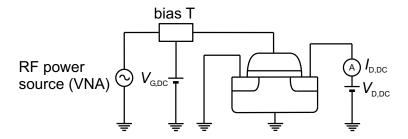

RF hot carrier experiments were performed on nMOSFETs in two different technologies. The type A devices were 90 nm process devices and the type B devices were processed in a 0.13  $\mu$ m process. The type A devices have a gate channel length of 0.10  $\mu$ m and the total gate width is 120  $\mu$ m, consisting of 4 identical cells each having 6 gate fingers of 5  $\mu$ m wide. The type B devices have a channel length of 0.13  $\mu$ m; the total gate width is 192  $\mu$ m, consisting of 8 identical cells each having 8 gate fingers of 3  $\mu$ m wide. All devices were laid out in a two-port ground-signal-ground configuration, optimized for RF measurements. The gate was connected to one signal pad and the drain to the other. The source was tied to the substrate and connected to the ground plane. The devices were connected on-wafer using Suss  $|\mathbf{Z}|$  probes. For each individual measurement a new device was connected.

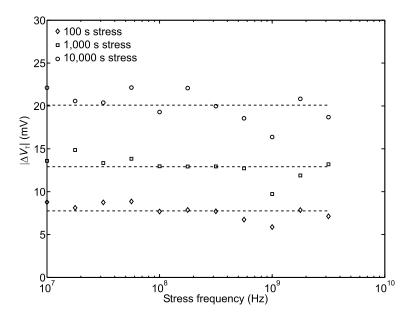

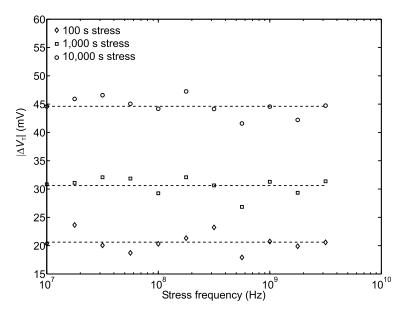

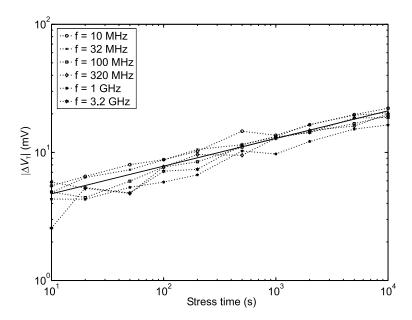

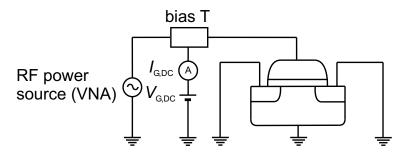

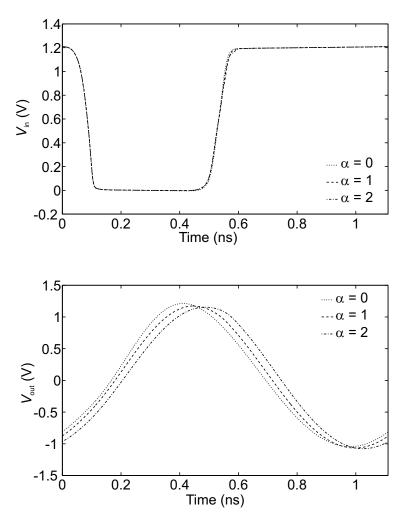

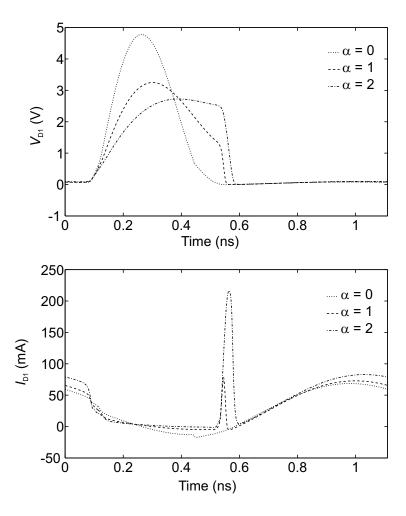

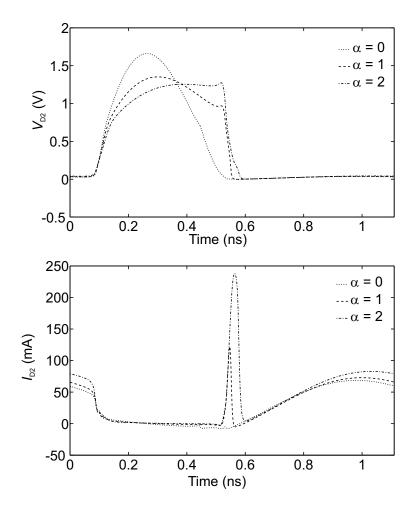

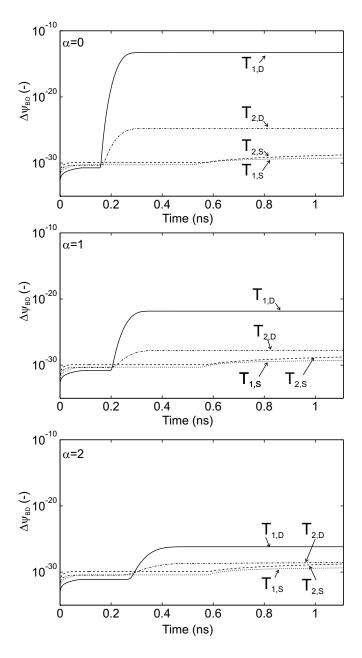

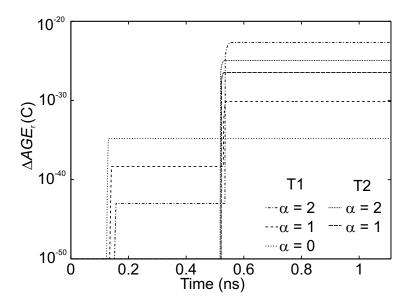

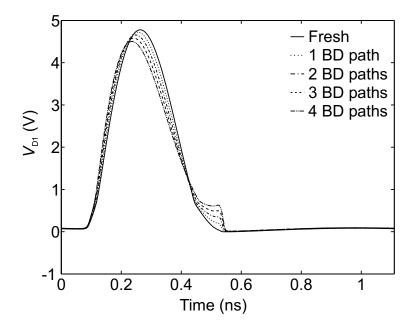

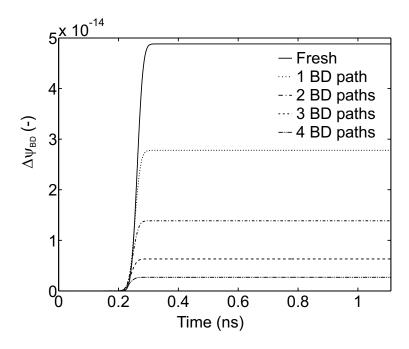

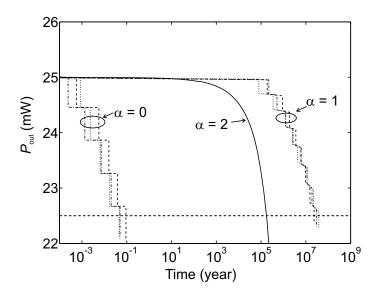

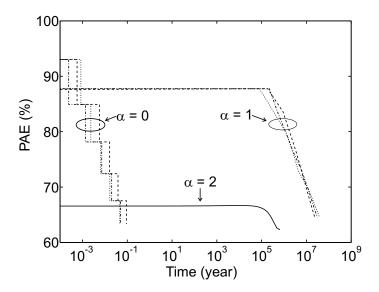

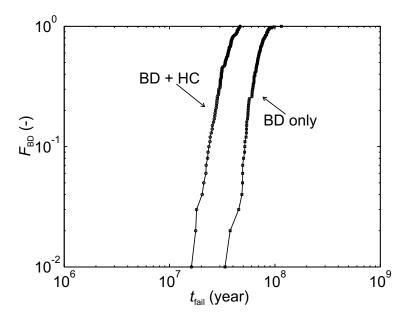

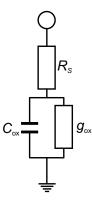

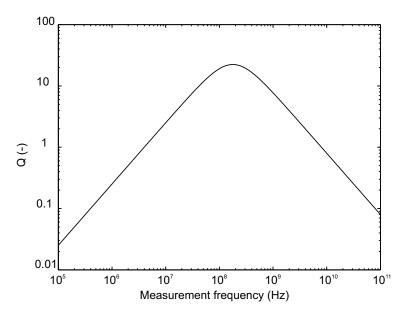

In figure 3.1 a schematic illustration of the measurement setup is given. The equipment used in the setup consisted of a Rohde & Schwarz ZVB 20 Vector Network Analyzer for generating the RF voltage and an HP4156A semiconductor parameter analyzer for the DC biasing and measurements. The equipment was connected, through an IEEE 488 bus, to a PC. The complete measurement procedure was controlled using Labview software.